# Assertion Based Verification of AMBA-AHB Using Synopsys VCS®

Akshay Mann, Ashwani Kumar

Abstract-The successof assertion based functional verification depends on the debugging environment associated with it. It helps user to get information about the environment in a refined manner. It also helps in realizing visualization support which tracks the behavioral aspects of the design under verification. This paper presents the design and verification of widely used AdvancedHigh-performanceBus(AHB)protocoloftheAdvancedMicroprocessorBusArchitecture(AMBA) using Assertion Based Functional Verification approach.This paper contributes as follows: (1) Designing of AMBA AHB protocol using System Verilog language in Synopsys VCS® tool. (2) Implementing assertions and analyzing the obtained coverage report. Hence, with this systematic description of the work done, we are able to automatically and completely synthesize and functionally verify an important and widely used industrial protocol.

------

Index terms-Functional Verification, Assertion, AMBA AHB, Synopsys VCS®, Functional Coverage.

## 1 Introduction

THE time taken for verifying the design is ▲ becoming tedious everyday as the complexity of the chip design is increasing exponentially. Nowadays, about 70% of the design time is needed for developing the verification environment [1]. The implementation of reused-based design, where the main blocks are recycled by using the existing designs, results in shifting of efforts from the design field to the verification field. Although, the present electronic devices have different functionalities, but the market demands new functionalities for which more efforts are required in design and verification from the same device. Also considering the constrained time-to-market pressures, new advanced techniques should be implemented [2]. Hence in this condition, it is important to reduce the verification time so as to speed up the whole development process [2]. But, on the other hand, the complexity of the design makes it difficult for the engineers to cover all the corner cases in minimum time. Therefore, to increase the design observability and to find and interpret its faults, a new technique is earnestly needed.

In the verification process, debugging is divided into three phases. The first step is error detection, which finds that the design is not working properly in a particular environment [3]. The second phase is error diagnosis in which the verification engineer identifies the exact location of the design which is causing the incorrect behavior [4]. The third step is error correction, in which the faulty part of the design is replaced by the corrected components. In today's scenario, Assertion-Based Verification (ABV) has been well accepted among the design and verification community as it plays an important role in the error detection phase [5]. Assertions aim to localize the failure and thus minimize the effort to locate the exact reason of the failure. However, assertions are mainly specified at the signal level, and thus do not automatically diagnose design behavior at abstraction (phase level, higher levels of transaction level) [6].

Assertion-based verification (ABV) is such a method, which combines assertion, simulation and formal techniques to the traditional functional verification [2]. Thispaperdescribesthe functional

verification of the AHB protocolof the Advanced Mi croprocessor Bus Architecture (AMBA). Throughoutt his work the given protocol is functionally verified by writing assertions for different AHB components. AMBA AHB architecture basically contains four different modules (Master, Slave, Arbiter and Decoder). This paper describes how assertions for different components help in the overall functional verification of the design.

The paper is organized as follows: Section 1 gives the introduction about assertion based verification and AMBA AHB architecture. Section 2 describes the AMBA AHB architecture and its different components. Section 3 gives the assertion based functional verification of AMBA AHB architecture using assertions for different modules and overall functional coverage of the design. Finally, section 4 concludes the work presented in this paper.

# 2. AMBA AHB Architecture

A widely used Advanced Microprocessor Bus Architecture (AMBA) aims at easing the component design by using the combination of interchangeable components in the SoC design [7]. It supports the reusability of intellectual property components, so that a least part of the design can become a composition.

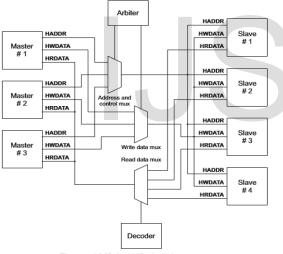

Fig. 1: AMBA AHB Architecture.

Fig. 1 shows the basic architecture of AMBA AHB. It consists of four main components- Master, Slave, Arbiter and Decoder. Arbiter is the main controlling component in the design. Decoder is used for decoding the addresses of different slaves. Master and Slave are used for performing read and write operations.

# 2.1 Components of AMBA AHB

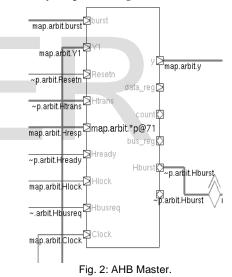

**1. AHB Master**- A master initiates the read and write operations by providing the address and control information to the interconnected design [8]. Only single master can access the system bus at

a time. Fig. 2 shows the schematic of AHB Master. When access is granted to any of the masters through Hgrant, address (HADDR) and control operations are performed. Also other signals like burst, Htrans, Hready and Hlock signals are activated to initiate read and write operations in AHB protocol.

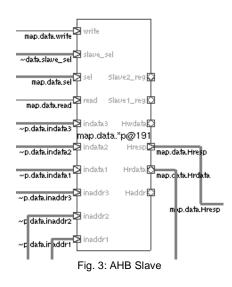

**2. AHB Slave**- The slave responds to the read and write operations of the master within the given address space range [9]. Also, it acknowledges to the master whether the read and write operations are successfully implemented. Fig. 3 shows the schematic of AHB Slave. A particular slave is selected by sel signal and data write (Hwdata) and read (Hrdata) operations are performed. The slave selects the data to be read from signals indata1, indata2 and indata3. After data is read by the slave through read signal, it acknowledges to the master and arbiter by respective signal.

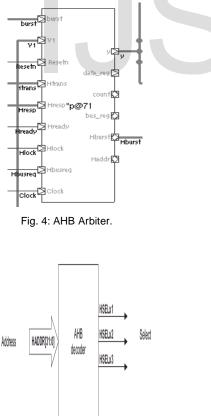

**3. AHB Arbiter-** An arbiter is used to grant access to a particular master for the bus at a time. The access can be granted to master according to any arbitration algorithm which decides the priority of the masters [10]. An AHB includes only single arbiter that would work as trivial in the single bus master systems. Fig. 4 shows the schematic of AHB Arbiter.

#### Fig. 5: AHB Decoder.

An arbiter is used for bus request (Hbusreq) and bus grant (Hgrant). The arbiter also initiates other signals like burst, Hready, Hlock, Hbusreq and Htrans when the master is ready for the data transfer. Arbiter is the main controlling component of the AMBA AHB design.

**4. AHB decoder**- The decoder decodes the address given by the master and enables the slave by selecting it to complete the transfer process [11]. A single centralized decoder is needed for all AHB implementations. Fig. 5 shows the schematic of AHB Decoder. From the corresponding addresses(HADDR), a decoder is used to select slaves (HSELx) from the address signals inaddr1, inaddr2, inaddr3.

# 3 Assertion based Functional Verification

Assertion based functional verification of AMBA AHB has been done by using twenty assertions. These assertions are implemented to find the overall functional coverage of the AMBA AHB design. First, separate assertions are used for different components (master, slave, arbiter and decoder) and their functional coverage is analyzed from the coverage report. After then, all the assertions are implemented to find the overall functional coverage of the design. The analysis of different components is described below.

3.1 AHB Master-Fig. 6 shows the assertion example of AHB master. The assertions used here are concurrent which depends on clock pulse. Property p7 initially checks the Hready signal and later on, it asserts Hresp and data\_reg signals to be true. Property p12 checks the Hlock and bus\_reg signals. Property p16 first assert the signal Resetn and then check other signals like y=idle, data\_reg, bus\_reg and count to be zero while property p17 separately checks the Hready signal. Fig. 7 gives the coverage report obtained after applying master assertions. The report shows the functional coverage along with code coverage (line, condition, toggle, fsm, assert and branch). The assertion waveform of the assertions and cover points a12, c12, a16 and c16 are shown in the fig. 8. The successful assertions are shown with 'up' arrows and failed assertions with 'down' arrows.

property p7; @(posedge Clock) (slt or ##1 s2t or ##1 s3t or s4t); endproperty

property pl1; @(posedge Clock) (Hready |-> Hresp && data\_reg==1'b0); endproperty

property pl2; @(posedge Clock) (Hlock |-> bus\_reg==1'b1); endproperty

```

property p16;

@(posedge Clock)

(Resetn |-> y==Idle or bus_reg==0 or

data_reg==0 or count==0);

endproperty

```

property p17; @(posedge Clock) (Hready); endproperty

Fig. 6: Assertion examples for AHB Master.

```

Design Hierarchy

SCORE LINE COND TOGGLE FSM BRANCH ASSERT

80.90 98.78 80.38 72.41 100.00 70.11 100.00 tb_aks3_proj

SCORE LINE COND TOGGLE FSM BRANCH ASSERT

85.62 91.75 79.36 72.41 100.00 70.11 100.00 uut

SCORE LINE COND TOGGLE FSM BRANCH ASSERT

80.08 92.20 78.89 42.25 100.00 70.22 100.00 arbit

78.55 90.54 84.27 70.29 -- 80,21 -- data

```

Fig. 7: Assertion report for AHB Master

| Sim | c11 | Success |      |

|-----|-----|---------|------|

| Sim | a12 | Success |      |

| Sim | c12 | Success |      |

| Sim | a16 | Success | **** |

| Sim | c16 | Success |      |

Fig. 8: Assertion waveform for AHB Master.

**3.2 AHB Slave-**The assertions examples for AHB slave are shown in fig. 9. The assertions used here are immediate ones which do not require any clock pulse. First immediate assertion checks the Hresp signal to be zero while the other assertion checks Hrdata signal. Fig. 10 shows the assertion report obtained when slave assertions are used. Since the immediate assertion are not covered under the assert coverage, it is shown as zero in the figure. Also other coverage is also less as compared to all the component assertions. Fig. 11 shows the assertion waveform for the assertions check\_assert, cover\_ack and read\_data\_check.

check\_assert: assert (Hresp==0) begin \$display("Working as expected"); end else begin #1 \$error("assert failed"); end cover ack: cover(Hresp==0); read\_data\_check: assert (Hrdata) begin \$display("Working as expected"); end else begin #1 \$error("assert failed"); end cover read data: cover (Hrdata); Fig. 9: Assertion examples for AHB Slave Design Hierarchy SCORE LINE COND TOGGLE FSM BRANCH ASSERT 70.82 98.81 0.00 76.43 100.00 78.85 -- tb aks3 proj ..... SCORE LINE COND TOGGLE FSM BRANCH ASSERT 56.35 28.26 0.00 74.67 100.00 78.85 -- uut ..... SCORE LINE COND TOGGLE FSM BRANCH ASSERT 44.84 58.12 0.00 48.44 100.00 75.76 -- arbit 62.96 92.86 0.00 74.79 -- 84.21 -- data Fig. 10: Assertion report for AHB Slave

Fig. 11: Assertion waveform for AHB Slave

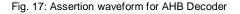

**3.3 AHB Arbiter-** The assertion examples for most important component in the AHB protocol, i.e. AHB Arbiter, are shown in fig. 12. The assertions used here are concurrent which depends on positive edge of clock pulse. Property p5 checks the Hbusreq signal through \$rose command, after that it asserts the grant (g) signal between second and fifth clock pulse. Property p6 checks the Hbusreq signal between two adjacent clocks by \$rose command and gives the result between second and sixth clock pulse while property gnt\_prop checks the grant (g) signal with the same procedure. Fig. 13 shows the assertion coverage report for AHB arbiter. As seen from the fig. 13, arbiter assertions gives the highest functional and code coverage excluding the toggle coverage. Fig. 14 shows the assertion waveform for the assertions a6 and a7 with their cover points c6 and c7 where successful assertions are shown by 'up' arrows.

check addr assert : assert(inaddr1 && inaddr2 && inaddr3) beain \$display("Working as expected"); end else begin #1 \$error("assert failed"); end cover addr : cover(inaddr1 && inaddr2 && inaddr3); check data assert : assert(indata1 && indata2 && indata3) beain \$display("Working as expected"); end else begin #1 \$error("assert failed"); end cover data : cover(indata1 && indata2 && indata3); Fig. 15: Assertion examples for AHB Decoder Design Hierarchy SCORE LINE COND TOGGLE FSM BRANCH ASSERT 87.91 99.89 84.38 76.43 100.00 78.85 -- tb aks3 proj ..... SCORE LINE COND TOGGLE FSM BRANCH ASSERT 86.27 93.48 84.38 74.67 100.00 78.85 -uut

> SCORE LINE COND TOGGLE FSM BRANCH ASSERT 80.18 93.75 82.98 48.44 100.00 75.76 -- arbit 85.02 92.86 88.24 74.79 -- 84.21 -- data

#### Fig. 16: Assertion report for AHB Decoder

| Sim | cover_addr      | Success   | 11 | 111 | INI  | 1111 | 111 | 111 | 111 | 1111 | Î |

|-----|-----------------|-----------|----|-----|------|------|-----|-----|-----|------|---|

| Sim | check_data_asse | rtSuccess | 11 | III | 1111 | TIII | III | 111 | 111 | 1111 | Ť |

| Sim | cover_data      | Success   | 1  | 111 | 1111 | 1111 | 111 | 111 | 111 | 1111 | Î |

The assertions waveform for cover\_addr, check\_data\_assert and cover\_data are shown in fig. 17.

### 3.5 Functional Coverage of AMBA AHB

The overall functional coverage of AMBA AHB design using all the assertions is shown in the fig. 18. All twenty assertions are implemented to find the functional as well as code coverage of the AHB design. The overall functional coverage is 89.92% while the line, condition, toggle, fsm, branch and assert coverage are 99.89%, 84.38%, 76.43%, 100%, 78.85% and 100% respectively.

Fig. 14: Assertion waveform for AHB Arbiter

**3.4 AHB Decoder-**The assertion examples for the centralized AHB decoder is shown in fig. 15 where immediate assertions are used. The first assertion check\_addr\_assert checks the addresses inaddr1, inaddr2 and inaddr3 while the second assertion check\_data\_assert checks the data indata1, indata2 and indata3. Fig. 16 shows the assertion report for the AHB decoder which gives the functional and code coverage for decoder assertions.

| SCORE LINE COND TOGGLE FSM BRANCH ASSERT                 |

|----------------------------------------------------------|

| 89.92 99.89 84.38 76.43 100.00 78.85 100.00 tb_aks3_proj |

|                                                          |

|                                                          |

| SCORE LINE COND TOGGLE FSM BRANCH ASSERT                 |

| 88.69 94.23 84.38 74.67 100.00 78.85 100.00 uut          |

|                                                          |

|                                                          |

| SCORE LINE COND TOGGLE FSM BRANCH ASSERT                 |

| 83.65 94.74 82.98 48.44 100.00 75.76 100.00 arbit        |

| 85.02 92.86 88.24 74.79 84.21 data                       |

|                                                          |

Fig. 18: Overall functional coverage report of AMBA AHB

Table 1 shows coverage analysis of AMBA AHB using different number of assertions. From the table, as the number of assertions increases, the overall functional and code coverage increases. Four assertions are used initially giving the functional coverage 65.23%. As the number of assertions increase to twenty, the functional coverage increased to 89.92%.

Table 1: Coverage Analysis table for AMBA AHB

| No. of  | Lin | Condit | FS | Tog  | Bran | Functi |

|---------|-----|--------|----|------|------|--------|

| Asserti | e   | ion %  | Μ  | gle  | ch   | onal % |

| ons     | %   |        | %  | %    | %    |        |

| 4       | 96. | 64.06  | 10 | 44.6 | 69.2 | 65.23  |

|         | 67  |        | 0  | 6    | 3    |        |

| 7       | 96. | 64.06  | 10 | 44.6 | 69.2 | 74.93  |

|         | 69  |        | 0  | 6    | 3    |        |

| 9       | 96. | 65.33  | 10 | 44.6 | 70.1 | 75.01  |

|         | 73  |        | 0  | 6    | 1    |        |

| 11      | 96. | 68.54  | 10 | 44.8 | 71.9 | 77.83  |

|         | 89  |        | 0  | 3    | 7    |        |

| 13      | 97. | 70.31  | 10 | 44.9 | 73.0 | 80.97  |

|         | 46  |        | 0  | 9    | 8    |        |

| 15      | 97. | 70.31  | 10 | 56.9 | 73.0 | 80.98  |

|         | 48  |        | 0  | 1    | 8    |        |

| 16      | 98. | 75.31  | 10 | 65.2 | 73.0 | 83.51  |

|         | 77  |        | 0  | 0    | 8    |        |

| 17      | 99. | 78.54  | 10 | 69.3 | 74.2 | 85.88  |

|         | 21  |        | 0  | 1    | 7    |        |

| 19      | 99. | 81.88  | 10 | 72.4 | 75.5 | 87.08  |

|         | 54  |        | 0  | 8    | 8    |        |

| 20      | 99. | 84.38  | 10 | 74.6 | 78.8 | 89.92  |

|         | 98  |        | 0  | 7    | 5    |        |

# 4 Conclusion

In this paper, assertion based functional verification of AMBA with AHB protocol is implemented using two types of assertions (immediate and concurrent). Initially, different components of AHB architecture (master, slave, arbiter and decoder) are described. After that, assertions are implemented separately for different components and obtaining their coverage results. While writing assertions, all the corner cases have been covered using immediate and concurrent assertions. For a 32-bit AHB bus, a number of test cases are required. Therefore, ABV is very helpful at pinpointing the bugs in the design with less time. Finally, all assertions are implemented altogether in the complete AMBA AHB architecture and the overall functional coverage report is analyzed. The result shows that the implemented method increases the observability and coverage of the design. Future work will focus on improving the functional and code coverage metric and approaching towards full coverage of the design.

**Acknowledgments:** I would like to take this opportunity to express my gratitude to the people whose assistance has been invaluable in this paper.

# References

- YashdeepGodhal, KrishnenduChatterjee, Thomas A. Henzinger, "Synthesis of AMBA AHB from Formal Specification: A Case Study", in *International Journal on* Software Tools for Technology Transfer, July 2011.

- [2] Yangyang Li, Wuchen Wu, LigangHou, Hao Cheng, "A Study on the Assertion-Based Verification of Digital IC", in Proc. of Second International Conference on Information and Computing Science, 2009, pp. 25-28.

- [3] A. Nandi, B. Pal, N. Chhetan, P. Dasgupta and P. P. Chakrabarti, "H-DBUG: A High-level Debugging Framework for Protocol Verification using Assertions", in Proc. of *IEEE Indicon Conference*, 2005, Chennai, India, pp. 115-118.

- [4] Roychoudhury, T. Mitra, S.R. Karri, "Using formal techniques to Debug the AMBA System-on-Chip Bus Protocol", Proc. of *IEEE Computer Society of Design*, *Automation and Test in Europe*, 2003, Munich, Germany, pp. 828 – 833.

- [5] P. Chauhan, E. Clarke, Y. Lu, and D. Wang, "Verifying IP core based system-on-chip designs", in Proc. of 12<sup>th</sup> Annual IEEE ASIC SOC Conference, 1999, India, pp. 27-31.

- [6] M. Benjamin, D. Geist, A. Hartman, G. Mas, R. Smeets, and Y. Wolfsthal, "A Study in Coverage-Driven Test Generation," in Proc. of 36th *Design Automation Conference (DAC'99)*, 1999, Los Angeles, USA, pp. 970-975.

- [7] ARM Ltd., AMBA specification (rev. 2) 1999, <u>http://arm.com/products/solutions/AMBA Spec.html</u>.

- [8] Han Ke, D. Zhongliang, S. Qiong, "Verification of AMBA Bus Model Using System Verilog", in Proc. of IEEE Conference on Electronic Measurement and Instruments (ICEMI '07), 2007, Xian, China, pp. 1-776, 1-780.

- [9] Y. Lin, C. C. Wang, I. J. Huang, "AMBA AHB Bus Protocol Checker with Efficient Debugging Mechanism", in Proc. of *IEEE International Symposium*

on Circuits and Systems (ISCAS 2008), 2008, Washington, USA, pp. 928 – 931.

- [10] M. Conti, M. Caldari, G.B. Vece, S. Orcioni, C. Turchetti, "Performance Analysis of Different Arbitration Algorithms of the AMBA AHB Bus", in Proc. of *IEEE Conference on Design Automation*, 2004, San Diego, USA, pp. 618 – 621.

- [11] L. Ivanov and R. Nunna, "Specification and formalverification of interconnect bus protocols," in Proc. of 43rd IEEE Midwest Symposium on Circuits and Systems, vol. 1, Aug. 2000, pp. 378-382.

# IJSER